## TD 4

### Exercice 1

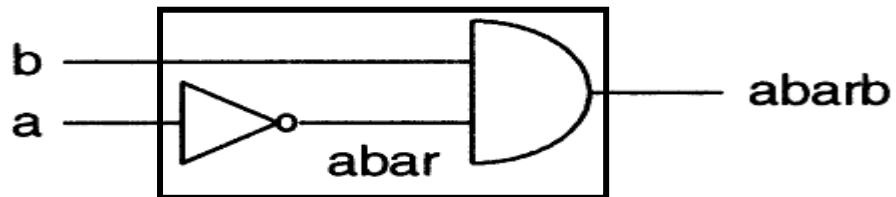

Soit le circuit suivant :

1. Ecrire le code VHDL (entity/Architecture) du circuit donné ci-dessus, tel que **a**, **b**, **abarb** sont de type bit.

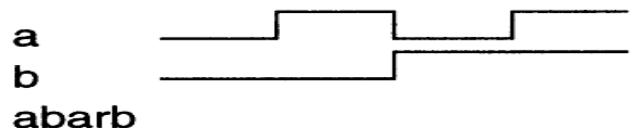

2. Compléter le chronogramme ci dessous.

### Exercice 2

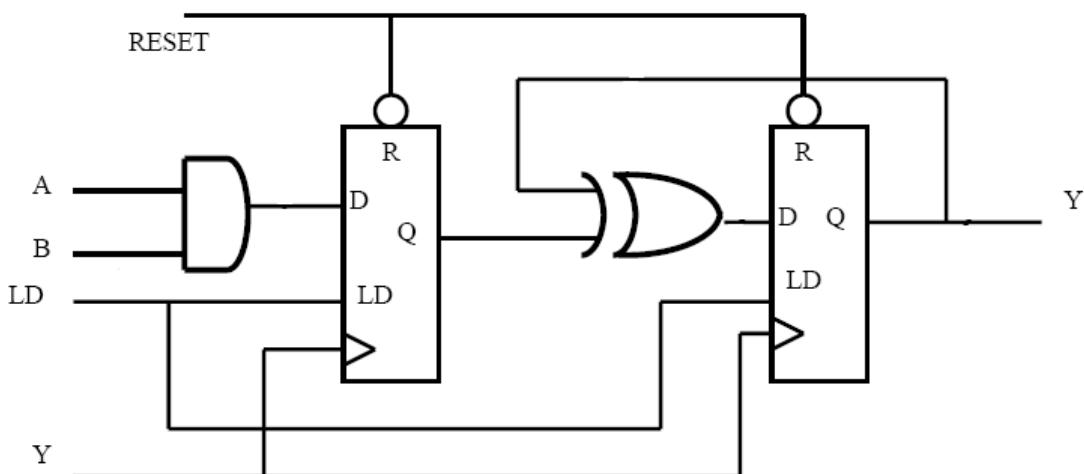

Ecrivez le code VHDL qui correspond au circuit de la figure ci-dessous. Supposant que :

1. Tous les signaux sont déclarés.

2. Les deux registres possèdent un chargement synchrone et une reset asynchrone.

### Exercice 3

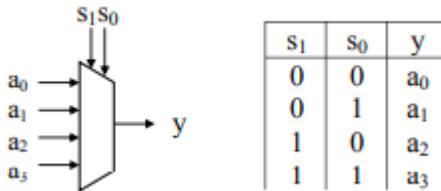

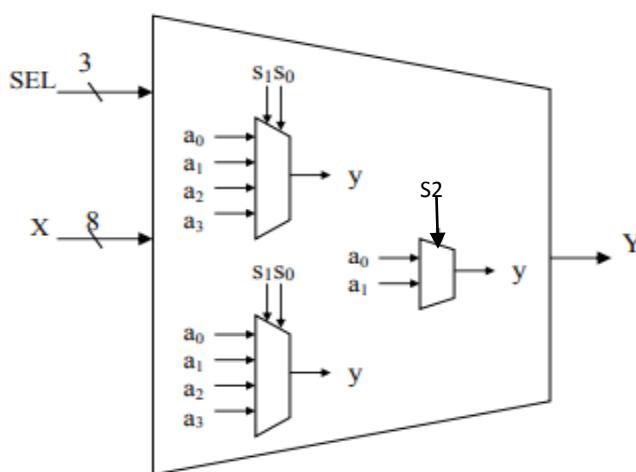

Soit une entité intitulée "mux4to1" qui est un multiplexeur 4 voies vers une, schématisé ci-dessous.

Le but est d'utiliser cette entité pour réaliser un multiplexeur 8 voies vers une. Des indications sur le schématique du circuit résultant sont donnée ci-dessous.

1. Donner la table de vérité du multiplexeur 8 to1.

2. Faire des interconnections nécessaires sur le schéma ci-dessus pour obtenir le mux8to1.

3. Compléter le programme ci-dessous pour générer ce multiplexeur.

```

entity MUX8TO1 is

port( ...,

...,

);

end MUX8TO1;

architecture RTL of MUX8TO1 is

component MUX4TO1

port(entree : in std_logic_vector(3 downto 0);

SEL : in std_logic_vector(1 downto 0);

Y : out std_logic);

end component;

signal ...

begin

...

end RTL;

```