## TD 1

### Question de cours

Répondre par vrai ou faux

1. Une seule entité peut avoir plusieurs architectures.

2. L'ordre de bit dans un vecteur n'est pas important.

3. La déclaration d'un signal interne, contient son nom, son mode, et leur type.

4. Chaque port doit être noté par son mode.

5. Une seule architecture peut avoir plusieurs entity.

6. Le signal qui connecte le système avec son environnement est noté comme un port.

7. Tous les signaux d'un système sont définis dans l'entité.

8. Tous les éléments d'un tableau en VHDL doivent être du même type.

9. Les opérateurs sont toujours définis pour des types particuliers.

10. Les opérateurs logiques peuvent être appliqués seulement sur un seul bit.

11. En VHDL, une architecture

- peut exister seul

- Ne peut exister qu'avec son entité de conception dédiée.

- Contient une description du comportement du circuit.

12. En VHDL, dans une architecture avant le mot clé begin, on peut trouver :

- Des instances de composants

- Des déclarations de composants

- Des déclarations des signaux internes

- Des instructions séquentielles

- Des instructions concurrentes

### Exercice 1

Soit l'extrait du code VHDL ci-dessous :

```

...

SIGNAL a: BIT;

SIGNAL b: BIT_VECTOR(7 DOWNTO 0);

SIGNAL c: STD_LOGIC;

SIGNAL d: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL e: INTEGER RANGE 0 TO 255;

...

a <= b(5);

b(0) <= a;

c <= d(5);

d(0) <= c;

a <= c;

b <= d;

```

```

e <= b;

e <= d;

```

- Déterminer les instructions VHDL légales et illégales.

### Exercice 2

Soit le code VHDL ci-dessous :

```

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY COUNTER IS

PORT ( clock : IN STD_LOGIC ;

RAZ : IN STD_LOGIC ;

Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0 )

);

END COUNTER ;

```

1. Dessiner la boîte noire correspondant à l'entité counter.

### Exercice 3

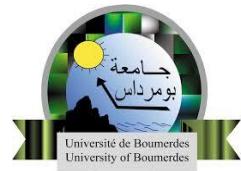

Soit les boîtes noires suivantes :

1. Écrire les entités correspondantes aux boîtes noires.

### Exercice 4

Soit le programme VHDL suivant :

```

1  entity muxtest is

2  PORT (in0          : IN  STD_LOGIC;

3        in1          : IN  STD_LOGIC;

4        in2          : IN  STD_LOGIC;

5        in3          : IN  STD_LOGIC ;

6        sel :  IN STD_LOGIC_VECTOR(1 DOWNTO 0);

7        s       : OUT STD_LOGIC

8      );

9  end muxtet

```

1. Deux fautes se sont glissées dans la même ligne : dites lesquelles.

2. Combien de bits sont contenus dans le bit vector **sel** ?

### Exercice 5

1. Relier chaque portion de code VHDL à l'emplacement où elle peut apparaître et à la description correspondante.

LIBRARY IEEE ;

Entity **demi\_add** is

Port (A : in STD\_LOGIC ;

B : in STD\_LOGIC ;

S : out STD\_LOGIC ;

R : out STD\_LOGIC );

End **demi\_add**;

S<=A xor B;

R<=A and B;

ARCHITECTURE IUT OF **demi\_add** is

use IEEE.STD\_LOGIC\_1164.ALL;

use IEEE.STD\_LOGIC\_ARITH.ALL;

use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

Begin

END IUT;

### Exercice 6

Soit A="110", B="111", C="011000" et D="111011"

- Trouver la valeur de l'expression :

$$((A \& \text{not } B) \text{ or } (C \text{ ror } 2)) \text{ and } D$$

### Exercice 7

Soit les équations suivantes:

$$Y1 = (a+b) ./ d.(c+(d+a.b))$$

$$Y2 = (c+d).(c+/a+b)$$

1. Ecrire ces équations en langage VHDL

Remarque : le / signifie le complément de l'entrée.